# **CCD & ELECTRONICS**

John C. Geary

### **OVERALL DESIGN**

- E2V CCD231: 4K X 4K, 15u pixels, 4 output amplifiers.

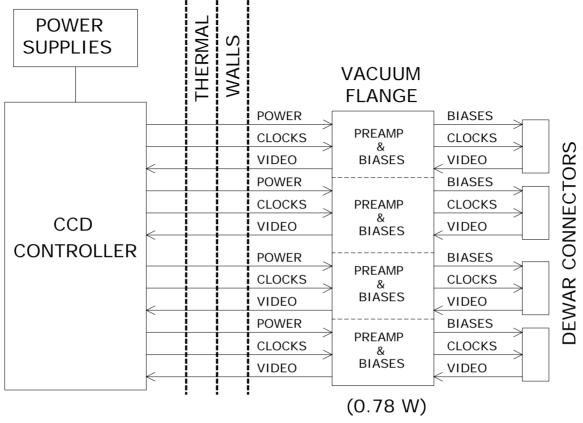

- Controller unit generating timing and digitizing signals outside the thermal enclosures.

- No active components inside the CCD dewar vessel, except for static-protection diodes.

- Preamplifier and bias generation circuits located just outside the vacuum connectors on the spectrograph tank.

#### READOUT MODES AND GAIN SETTINGS

- Pixel rates of 100kHz up to 400 kHz are contemplated (question: is 400 kHz really necessary/desireable? This has some design impacts).

- Need an overall charge resolution of 0.7-1.0 e- to adequately sample the noise floor. Limits saturation charge to ca. 60k e- or less for a 16-bit system.

- Lesser gain for bright scenes (comparison spectra) can be provided. What factor is desirable?

- Full well may be as high as 350k e- (CCD44-82 has about 200k e-). What fraction of this do we really need to cover at reduced gain?

- Can read out through any single output, any pair of outputs, or all four outputs simultaneously.

- Readout modes may impact digital analysis and ultimate accuracy (see discussion below).

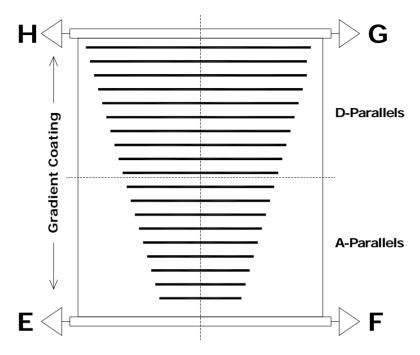

## **CCD231 Organization**

The CCD231 has split parallel organization, with split serial registers as well. It has been suggested that we orient the CCD such that the direction of main dispersion is along the serial register, as serial transfer efficiency is thought to suffer less than parallel transfer from charge level effects. But, does this preclude using the device in split-serial readout mode, where any small charge transfer inefficiencies would appear in opposite directions on the two halves of each spectral order? Even if this does not ultimately introduce velocity inaccuracies, it is likely to require independent processing of wavelength solutions for each half of the spectrum.

#### DIAGRAM OF THE ELECTRONICS LAYOUT

We envision putting the most noise-sensitive elements for each quadrant of the CCD on the 150mm vacuum flange that carries the hermetic connectors into the spectrograph tank. Not only the preamplifiers for each of the four channels but also low-noise bias voltage regulators will be integrated into a well-shielded, highly crosstalk-immune module. Power dissipation will be about 780mW if pixel rates of 200kHZ or less are used, increasing to about 1.0 W if 400 kHz is necessary. This constant heat load can be dumped via conduction to the spectrograph tank wall, or dumped to the local air, or extracted using hoses to the outside room (TBD).

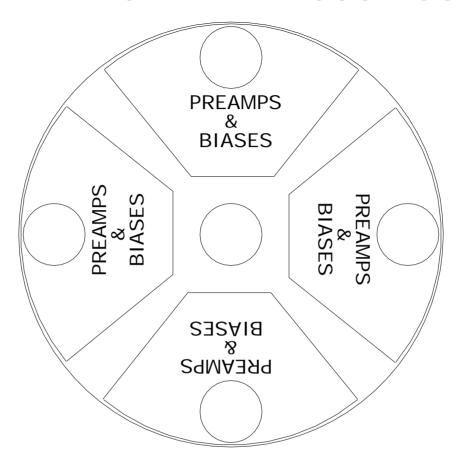

#### THE 150MM FLANGE WITH VACUUM CONNECTORS

Each quadrant of the CCD will be serviced by one hermetic connector and associated cable down to the CCD dewar (18 pins each should suffice), with the preamp/bias printed circuits just outside the vacuum. A central connector is provided for thermal and shutter control, but we are unsure about the details of the latter control signal specification or whether it needs to enter at this point.

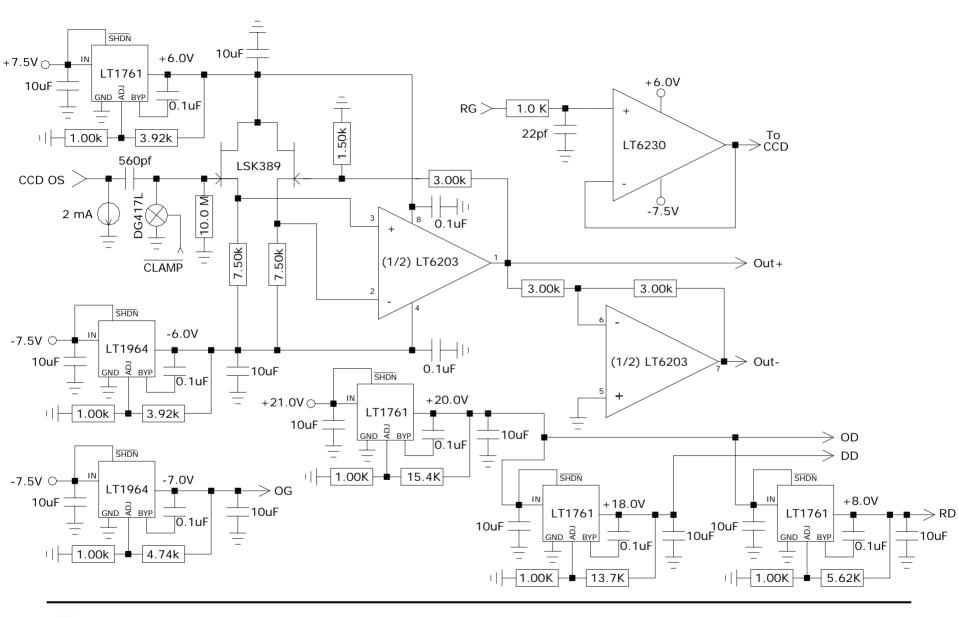

#### PRELIMINARY SCHEMATIC OF THE PREAMP/BIAS CIRCUITS (ONE CHANNEL)

#### **OUTSTANDING DESIGN ISSUES/QUESTIONS**

- 1. We do not yet have a detailed description of the thermal control system for the cryostat head, such as position and type of sensors and heaters and the detailed setup of the Lakeshore controller for these.

- 2. How simple or complex must the heat dump from the preamplifiers be (0.8 1.0 W) at the 150mm tank flange)?

- 3. What is the optimal partitioning of work between Cambridge and Geneva/ESO for the mounting of the CCD231 and the internal wiring of the cryostat dewar?

- 4. What is the nature of the control signal(s) needed for the shutter and what is the best routing of cables for this function?